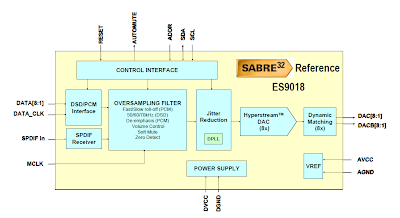

ES9018Sブロック図

ES9018K2Mブロック図

| Device | ES9018S | ES9018-2M |

| price (1000個ロット時) | $39 | $12 |

| ch | 8ch | 2ch |

| 32bitDAC | Yes | Yes |

| sampling rate | up to 1.536MHz | up to 384Hz |

| DSD | Yes | Yes |

| Pakage | 64-LQFP(10mm×10mm) | 28pinQFN(5mm×5mm) |

| operational power | 3.3V/1.2V 150mW(8ch) | 3.3V/1.8V 40mW以下 |

| Standby power | - | スタンバイ時では1mW以下 |

| DNR | 135dB(mono) 133dB(2ch)129dB(8ch) | 127dB(2ch) |

| THD+N | -120dB | -120dB |

| Jitter | Time Domain Jitter Eliminator | Time Domain Jitter Eliminator |

| SPDIF | Yes | Yes |

| ASRC | Yes(OFF不可) | Yes(OFF可) |

| OSC | 外部 | 内蔵 |

ES9018の2ch版は従来はES9012という品名を用いていますが、2chなのにES9018K2Mという品名でまぎらわしいことになっています。おそらくES9018のネームバリューにのっかるためでしょう。

ASRC内蔵しての有効/無効制御によりシンクロナスモードとアシンクロナスモードの、2つの同期モードをサポートできるようにしたようです。が、この意図はよくわかりません。

比較表は解釈が間違っている部分もあるかもしれません。

主としてモバイル向けへ適用しやすいように2chに絞りチップサイズの小型化、低消費電力化、OSCの内蔵による周辺チップ削減などを行ったもので、価格は安くなっているようですが特性は若干悪くなっています。新しいチップということで期待して見ましたが、据え置き用としてはES9018Sから変更を考えることもなさそうです。

*赤字 加筆・訂正

*下記追記

*赤字 加筆・訂正

*下記追記

bunpeiさんのご指摘により、ES9018SはASRCを搭載しており(多分)OFFにできないとのことで、About Jitter: Digital Audio's weakest link October 2011にASRCについての記載がありました。この資料よりクロック構成は下図の様になっているようです。

ES9018SのASRCとクロック構成

WM8804 / WM8805の資料A high performance S/PDIF receiverではASRCは必ずしも好ましくないと書かれいます。

"Whilst the use of sample rate converters is widespread it is not necessarily optimal [1].

Recent work has investigated the design of different filter types for audio data [2] and there is anecdotal evidence to suggest that different sample rate converters sound different."

この記述を見たばかりで、それ以前からもASRCは使わないように構成したいと考えていたので、ES9018はASRC内蔵と知りちょっとショックです。まあ、通常のASRCとは制御が異なるようですが..まだ全然理解できていません。

Bunpeiです。

返信削除ES9018ではASRCしかありませんでした。たとえI2S/DSD信号に同期したマスタークロックを入れても、ASRCのDPLLを止めることはできず、No Bandwidthでのロック外れが発生していました。ES9018-2Mでは、ASRCのDPLLを止めるモードが追加され、同期のマスタークロックを使った場合は、いつも完全にロックするという、いわば当たり前のことが行われるようになったということですね。

Bunpeiさん

削除ES9018については、内部仕様が詳しくは開示されておらず、どう使用するのがより良いのか考え方がわからず困ったものです。

ES9018Sのデータシートには、ASRC搭載とはなにも書かれていないようですが、ASRC搭載している情報はどこかに書かれているのでしょうか?

MCLKとBCLKが同期を前提としていないことから、ASRCが使われていると考えるのが妥当なところだとは思いますが、独自技術のJitterリダクションシステムを搭載と謳っているので、独自のPLL技術等でASRCなしでもうまく制御できているものと思っていました。

ES9018K2Mのブロック図にはASRCと明記されていて、このような表現だとES9018SにはASRC搭載なし、ES9018K2MはASRC搭載していてASRC有効/無効が選択できるようにしか見えず困ったものです。

SFORZATO DSP-03がNoBandwidthで動作成功させたことをdiyAudioに投稿されて、SFORZATOのコメントは、”I2S信号を同期したMCLKでリタイミングしただけ"とのことようですが、信用出来ないというようなコメントも見られ、私もなんとなく懐疑的に思っております。

Bunpeiです。

返信削除ES9018について、DACの設計者で、情報が少ないとこぼす人がいますが、それは短期間に確実に設計して応用製品化しなければならないプロの方の言い分であって、DIYユーザにとっては、情報の少ないことこそが醍醐味だと思っています。隠しレジスタも含めて自分でいろいろ試行錯誤して楽しめるのですから。それに例えばWM8741ならもっと公開されているのかというと、私はそうとは思いません。

ES9018を知るには、もう一度、White Paperを同社のサイトからダウンロードして、じっくりと読まれることをお勧めします。ASRCと直接的に記述されていなくても、書かれている内容はASRCそのものです。

SFORZATOのDSP-03の件は、疑いをさしはさむ余地はないと思います。quspのおっさんのいうことのほうがずっと信用できません。

Bunpeiさん

削除まだES9018についてあまり詳しく調べておらず、データシートとBlogなどで見た情報だけで判断し、White Paper等のあることを忘れていました。

>SFORZATOのDSP-03の件は、疑いをさしはさむ余地はないと思います。

MCLKとBCLKを同期させること自体は、かなりの人が試みていると思いますが、そうなるとBCLKがMCLKに対し極限までジッタが無いところまで追い込めばのNoBandwidthでも問題なく再生できるのに対し、みなさん比較的長い配線ラインのまま実験していたりすることによって残留ジッタ等がまだクリアできるところまでは追い込めていないからということになりそうですね。

通常の設計であればI2SのData、LRCKは一旦チップ内に取り込み直後にBCLKでリタイミングするので、MCLKでリタイミングするのはI2S全信号ではなくBCLKだけで効果があると想定しています。

データシートは測定条件を明記してどの測定器をどのセットアップで使ったか書いていない物は信頼性に欠けていて無意味です。

返信削除ESSのはデータシートではなく暫定情報程度のものです。

新しいチップのASRCは通常のASRCが入っているのかもしれませんね。

データ上の数字はES9018Sの1chと同じなのでステレオで使ってアンバランスだとこちらの方が楽に作れそうです。

パッケージがQFN28なのでデカップリングしやすいでしょうし電源も1.2Vが無いのこちらの方が楽でしょうね。

rtm_iino さん

削除ES9018SではASRCが必ず働くようなので、ES9018K2MではBCLKとMCLKを同期させる使い方に対応できるようにASRCバイパスさせられるように改良したのではないかと推測します。

アンバランスだとというのは、バランスだと何か複雑になる要素が考えられるのでしょうか?

モバイル向けで低消費電力狙っているなら、1.8Vではなく1.2Vを選択肢そうなものですが、1.2Vだとなにか不都合があったのだと思われますが、想像がつきません。

>I2S信号を同期したMCLKでリタイミングしただけ

返信削除これはNo bandwidthを狙うのでなくても御利益があるようです。うまくすれば概ね大元の発振器+リタイミング回路由来のジッタだけに収まるとか。

diyAudio内でIancanadaさんが実際に計測までされています。

その上で、単なる推測ですが差動伝送上で行うのがベストではないかと思います。実際ロジックIC等でも差動(ECL)の方が遥かに優秀です。

わかっている限りではNo bandwidthをやろうとするとMCLK周波数が大きく制限されるので、これが個人的にはちょっとイヤな感じですが、

2Mではこのような制限なしにDPLLを止められるのでしょうか。

Y.Oさん

削除>これはNo bandwidthを狙うのでなくても御利益があるようです。

NoBandwidthでなければBCLKとMCLKが同期している場合は、問題なく再生できるのではないかと思いますが、ご利益というのはリタイミングによりジッタ量の低減が確認されたということでしょうか?

装置間は差動というのは同意です。必須と言っても良いと思います。

ただ、私のようにマルチチャネルを想定せずDAC 1台だけで良いなら、差動かどうかよりDACチップ近傍にCXOを配備するのが基本で、DACチップのクロック入力がアンバランスなので無理に差動にこだわるよりはCXOの配置の方を優先したほうが良いと思います。

http://www.diyaudio.com/forums/digital-line-level/192465-asynchronous-i2s-fifo-project-ultimate-weapon-fight-jitter-195.html#post3312929

削除スレッドが長くて探し出すのが大変なので貼っておきます。wm8805出力直後と実測でのジッタ量の比較です。

記事中SCK(いわゆるBCK)jitter after FIFO と書かれていますが、詳しくはFIFOから出た直後でリタイミングしたものです。

Y.O さん

削除diyaudioの測定条件がわかりませんが、測定時間が長ければこのようは測定結果になるのではないかと想像します。

WM8805のジッタリダクションシステムだとElastic Bufferのデータ量の増減に合わせて周波数を調整するのでCXOに比べればpeak.to.peak period jitterはある程度大きくなるのは自明だと思います。ただその周期が10Hzより遅く聴感に影響しにくい領域にしているのがミソだと考えています。

比較対象のI2S FIFOでMCLKに載せ換えてあげればジッタは良くなりますが、遅延が大きくなる問題がつきまといますので、遅延を気にしない場合はFIFOを、遅延を気にするならFIFOをバイパスのチョイスが良いのかもしれません。

Y.O = wktk_smile さま

返信削除No Band Widhで音が切れるのはジッター量には関係無さそうです。

WM8805のTOSLINK→I2S出力やAmaneroのジッターの多いクロックでも

BCKの4倍のマスタークロックだとデータレートの32ビット周期で音は切れるものの音楽再生できています。

逆に非同期の100MHzなどを使うと安定度の悪いクロックならLowestでもブツブツに切れます。

rtm_iino さん

削除I2S信号を同期したMCLKでリタイミングしただけNo bandwidthの再生に成功というのは、データレートの32ビット周期で音は切れる現象が解消されたことを意味していると思います。

SFORZATO DSP-03だけがNoBandwidthでの再生に成功しており、他ではうまくいかないのであれば、周期的なリセットの原因はジッタ量の差となるものと思います。

rtm_iino さんのES9018 DACでは、BCLKをMCLKでリタイミングできますでしょうか?

I2S全信号対象ではなくBCLKだけで良いなら、Si5326等によりMCLKとBCLKを生成すればリタイミングしたことと同じ効果になると思います。

kou さま

返信削除仕事が忙しくてES9018Sに同期クロックをまだ入れていませんがTackbonさんの所で使っているSi5338の位相差は無調整で600pS以下だったと思います。

HPのWオーブンのOCXOからのクロックですので通常で考えると十分すぎるはずですが

それでもロックしないとなると何か一工夫必要なのかもしれません。

FN1242Aを一度聞いてみてください。

近日中にタンタルとPMLCAPを共用できるランドパターンを変更した物を作る予定です。

さっき久々にWindows7のブルー画面になってしまいこの週末は地獄です。

セーフモードからネットに繋がるのですが通常起動ではクラッシュダンプの連続で、復元ポイントを1週間以上前まで戻してもやはりまだブルーです。

イベントログで確認していますが今のところ原因不明。

この際Windows8をインストールするという方法で逃げてしまうというのもありかもしれません。

SolarisやLinuxをメインで使えるならそれが一番ですがWineで動かないソフトも多いので駄目ですね。

先日Windows UpdateでIEがクラッシュした友人のマシンを修復しましたがどうも今回もそのパターンに近い感じがします。

rtm_iinoさん

削除位相差は0に近い方が良いとも限らないと思いますので、位相を360度少しずつ変えてみると改善する可能性もあるかと思います。

また、SFORZATOは、筐体にもコストをかけているようですから、シールドや電源ノイズ対策、ジッタ対策がかなりの完成度で、だからこそ実現できた可能性もありそうです。

Bunpeiです。

返信削除ES9018のDPLLをNo Bandwidthにしたときのロック外れに関しては、私は以下のように推測しています。これはあくまでも推測であり、データシートや同社の技術資料・インターネット上の情報による確たる根拠はありません。

I2S/DSD信号に同期したマスタークロックを使った場合は、常識で考えるとロック外れの起こる余地はありえません。

ここで、同期というのは、I2SではBCLK、DSDではDSDCLKとマスタークロックの間の関係のことです。

しかし、現実にはロック外れが起こっています。このロック外れは、統計的なジッターというよりはむしろ、外乱ノイズ的なものでBCLK/DSDCLKのカウント数が予期するものと違ってしまったときに起こると推測しています。では、どのようにカウントしているかというと、以下のように考えます。この前提として、ES9018内部には絶対的な周波数のカウンタとそのために必要な発振器は内蔵されておらず、すべてはマスタークロックを基準として相対的に処理されていると仮定します。

内部には、マスタークロックをカウントするカウンタとBCLK/DSDCLKをカウントする2つの32ビット符号無整数のカウンタがある。

マスタークロックカウンタが2の32乗をカウントした時点のBCLK/DSDCLKのカウント値が、DPLLのカウント値となる。このカウント値のラッチされたものはレジスタ値として読み出せる。

No Bandwidthの場合は、DPLLのカウント値が前回の値と同一でなければロック外れと判定される。したがって、外来ノイズ等の影響でたとえ、2の32乗個に対して1個でもずれがおこるとロック外れと判定されてしまう。

では、No Bandwidth以外の場合はどうかというと、ロック外れ判定の閾値がおそらく2のべき乗単位で大きくなる。また、2つのカウンタのカウントは実際の入力パルス信号1個に対して2のべき乗倍を掛けた形でカウントされる。したがって、DPLLのカウント値を求めるのに要する時間は2のべき乗のオーダーで短くなる。DPLLの確定値を出す場合の、ゲイン的な係数も2のべき乗単位で大きくなり、変動は大きくなる。このため、聴感上の品質が低下する。

>DPLLの確定値を出す場合の、ゲイン的な係数も2のべき乗単位で大きくなり、変動は大きくなる。このため、聴感上の品質が低下する。

削除同期したMCLKでもここが変動することで聴感に影響するということはやはりこのカウント値がリサンプリング動作に影響しているのでしょうか。

例えば、整数倍からごく僅かに外れた周波数に変換されるとか?

Bunpeiです。

削除ES9018のDPLLというのは、本当の意味のPLLではなく、そういう呼び方をしているだけだと思います。だから物理的にDPLLまたはアナログPLL発振器が内部にあるわけではない。また、マスタークロックをさらに逓倍しているという話も聞かないので、「整数倍からごく僅かに外れた周波数に変換される」ということはないと推測します。

しかし、DPLLのカウントの実測値がずれると、それに応じてDPLLの設定値が自動調節によって動くのだろうと思っています。

bunpeiさん

削除マスタークロックをカウントするカウンタとBCLK/DSDCLKをカウントする2つの32ビット符号無整数のカウンタが1つでも差がある場合にロックはずれするという説は、合っているように思います。

その原因はbunpeiさんの想定の"外乱ノイズ的なもの"と、もうひとつ考えられるのは"MCLKとBCLKの位相関係"がある条件に入っていない場合というのもあるかと思います。

MCLKとBCLKの位相関係によっては、完全に同期していてもカウンタのロード(リセット)タイミングとBCLKの位相によってMCLKのカウンタと必ず1つカウントがずれてしまうことになるというものです。MCLと同期したI2S信号をMCLKでリタイミングするということは、MCLKに対するBCLKの位相がリタイミング前と後で必ず変わるはずですので、リタイミングにより"MCLKとBCLKの位相関係"がある条件に入る/入らないが変化した可能性もあるかと思います。

"ES9018のDPLLというのは、本当の意味のPLLではなく、そういう呼び方をしているだけ"

ブログに貼りつけた"ES9018SのASRCとクロック構成”の図の中央の位相比較とDCOの部分は搭載されている可能性は高いと思います。

MCLKの1クロック単位に出力周波数は調整するのもではないかと思います。

Bunpeiです。

削除確かにkouさんがおっしゃるように、MCLKとBCLKの相互のタイミングがきわどいところにあると、数えたり数え落としたりが起こりえて、良くないと思います。AIT LABの角田さんは、nsオーダーでの相互のタイミングの調整が重要と言っておられますね。

ブログに貼り付けられたESSのプレゼンテーション資料の図は、良く見ると少しおかしいように感じられませんか?

ASRCの箱にDAC側のOscの矢印が伸びていないでしょう。ASRCというのは、DAC側のOscに変換するわけですから、必ずそちらがつながっているべきだと思うのですが。

Bunpeiさん

削除PLLは使っていないような記述もあり、確かにPLLが無い可能性も高そうです。

図はデフォルメされて正確性はないものとして見ないと間違って解釈しそうですので、そういう意識を持ちながら調べてみたいと思います。