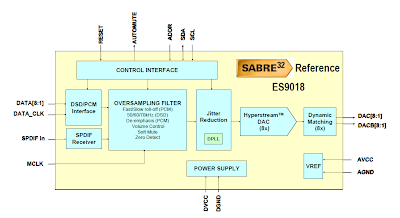

ES9018Sブロック図

ES9018K2Mブロック図

| Device | ES9018S | ES9018-2M |

| price (1000個ロット時) | $39 | $12 |

| ch | 8ch | 2ch |

| 32bitDAC | Yes | Yes |

| sampling rate | up to 1.536MHz | up to 384Hz |

| DSD | Yes | Yes |

| Pakage | 64-LQFP(10mm×10mm) | 28pinQFN(5mm×5mm) |

| operational power | 3.3V/1.2V 150mW(8ch) | 3.3V/1.8V 40mW以下 |

| Standby power | - | スタンバイ時では1mW以下 |

| DNR | 135dB(mono) 133dB(2ch)129dB(8ch) | 127dB(2ch) |

| THD+N | -120dB | -120dB |

| Jitter | Time Domain Jitter Eliminator | Time Domain Jitter Eliminator |

| SPDIF | Yes | Yes |

| ASRC | Yes(OFF不可) | Yes(OFF可) |

| OSC | 外部 | 内蔵 |

ES9018の2ch版は従来はES9012という品名を用いていますが、2chなのにES9018K2Mという品名でまぎらわしいことになっています。おそらくES9018のネームバリューにのっかるためでしょう。

ASRC内蔵しての有効/無効制御によりシンクロナスモードとアシンクロナスモードの、2つの同期モードをサポートできるようにしたようです。が、この意図はよくわかりません。

比較表は解釈が間違っている部分もあるかもしれません。

主としてモバイル向けへ適用しやすいように2chに絞りチップサイズの小型化、低消費電力化、OSCの内蔵による周辺チップ削減などを行ったもので、価格は安くなっているようですが特性は若干悪くなっています。新しいチップということで期待して見ましたが、据え置き用としてはES9018Sから変更を考えることもなさそうです。

*赤字 加筆・訂正

*下記追記

*赤字 加筆・訂正

*下記追記

bunpeiさんのご指摘により、ES9018SはASRCを搭載しており(多分)OFFにできないとのことで、About Jitter: Digital Audio's weakest link October 2011にASRCについての記載がありました。この資料よりクロック構成は下図の様になっているようです。

ES9018SのASRCとクロック構成

WM8804 / WM8805の資料A high performance S/PDIF receiverではASRCは必ずしも好ましくないと書かれいます。

"Whilst the use of sample rate converters is widespread it is not necessarily optimal [1].

Recent work has investigated the design of different filter types for audio data [2] and there is anecdotal evidence to suggest that different sample rate converters sound different."

この記述を見たばかりで、それ以前からもASRCは使わないように構成したいと考えていたので、ES9018はASRC内蔵と知りちょっとショックです。まあ、通常のASRCとは制御が異なるようですが..まだ全然理解できていません。