BDP-S370=>DN-HDMI4000ASルートで176.4kHz 24bit再生について確認してみました。

SDRAMバッファモードを使用した下図の構成での再生になります。

結果うまく再生できているようです。

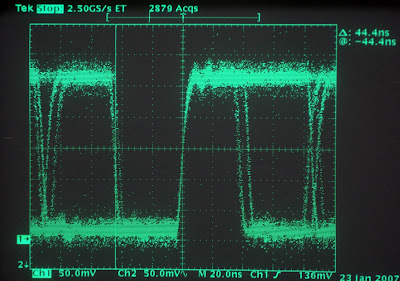

まず、どうしようかと困っていたTOSの176k受信についてですが、TORX-147は、仕様上96kHzまでしかサポートできないことになっていますが、176.4kHzで問題なく受信しているようです。

ということで、SPDIF 192kHzまでの伝送にTORX1701を持ち出す必要はなくなりそうです。

BDP-S370=>DN-HDMI4000AS=>MultiDAC(SDRAMbuffer_mode)=>PC=>MultiDAC=>BuffaloII

途中、DN-HDMI4000ASからPCのRayDATへ接続しているSPDIFのラインを抜いたのですが(上図の一番上のライン)、その後、ノイズのみで全く再生できなくなり、何が何だかわからなくなりました。

その後いろいろやっているうちにSPDIFのラインを元のように接続すると何事も無く再生できるようになりました。

DN-HDMI4000ASにとって出力であるSPDIFが何故影響するのかさっぱりでしたが、受信端側であるRayDAT側ではなく、送信端であるDN-HDMI4000AS側のコネクタを抜いた場合は何の問題も無く再生できることがわかりました。

要は、SPDIFのケーブルがアンテナになり、TOSにも多大に影響をあたえ、全く同期がとれないほどのノイズを生み出していたようです。

未使用ケーブルは抜いておくことが肝要のようです。

RayDATのSetting画面

残りの問題点として、RME RayDATが176.4kHzモードにしているのにもかかわらず、44.1kHzモードで立ち上がってしまうことです。

どうも96kHzのときは問題なかったのですが、176.4kHzにした場合、ADAT受信ポートをClockMasterにしておくと、44.1kHzに、RayDAT自身をMasterにするときちんと176.4kHzになるようです。

原因は上図のInput Status/Pref.Sync Ref のADAT1の表示が44.1Hzになっていますが、ADATのレートを何らかの方法で通知しているようで、それができていないためと推測されます。

たしか、RayDATの送信をRayDATの受信に接続した場合は、この表示が設定レート通り表示されていました。

このレート伝達手段を調査あるいは解析して実装してあげないと、毎度RayDAT自身をMasterにする操作が必要になるようですので、早めに解決したいところです。