そこでTPS7A47 LDO Voltage Regulator 基板 Largeをベースに改版することにしました。

主な変更点

・出力端子を4ペアに

・スタックする場合、スペーサーの支柱で入力電源ラインを分配

・電圧設定をSMT Padからショートピン(1.25mmピッチ)に変更

・ヒートシンク穴位置を調整し、秋月放熱器(ヒートシンク)20x25x20mm,

放熱器(ヒートシンク)16x25x16mmあたりの取り付けが支障なく付けられるように

・10μFのパスコンのサイズ

①出力10μFコンデンサを1個増やしPadサイズを大きくしました。

ルビコン薄膜高分子積層コンデンサ(PMLCAP) 10μF25V を2個を

3つのPadに2つ並べれば実装できるように *3/23

②入力10μFコンデンサのPadにPMLCAP 10μF25V 1個追加(裏)*3/23

TPS7A47 LDO Voltage Regulator 基板 Large V2 回路図 3/23差替

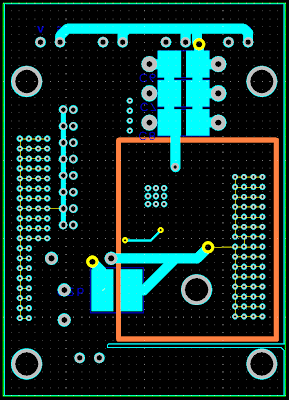

TPS7A47 LDO Voltage Regulator 基板 Large V2 A面 3/23差替

TPS7A47 LDO Voltage Regulator 基板 Large V2 B面 3/23差替

オレンジの枠は放熱器(ヒートシンク)20x25x20mmをつけた場合の実装位置

TPS7A47 LDO Voltage Regulator 基板 Large V2 A面3D 3/23差替

TPS7A47 LDO Voltage Regulator 基板 Large V2 B面3D 3/23差替

希望があれば50枚 or 100枚発注します。Blogerには、管理者のみへのコメントは出来ないようなので、以前のブログ http://multidac.blog130.fc2.com/ かTwitterのダイレクトメッセージで連絡ください。